alarm clock

$10-30 USD

Concluído

Publicado há aproximadamente 9 anos

$10-30 USD

Pago na entrega

Design the control logic for an alarm clock (for simulation purposes 20ns simulation = 1 minute real time – this can be adjusted somewhat for simulation purposes).

a) Use multiple input signals (alarm set input, the snooze, and the alarm time).

b) The design will contain one output (Alarm_On). A logic high at the output represents the alarm being “on”.

c) An input will be used to set the alarm off.

d) When the simulation starts, a counting mechanism will start counting (representing/roughly simulating a clock).

e) If the alarm set input signal is high, then the alarm should turn on when the count equals the preset alarm value. If at any point during the simulation the alarm set input is switched off, the alarm should turn off by the next complete clock cycle.

f) If the snooze button is activated (assume that snooze is a pulse that is at least one full clock cycle in duration) the alarm should turn off and then turn back on after 5 minutes.

g) Repeat snooze button simulations (pulses) should cause the same behavior in the circuit.

h) If at any time the alarm set input signal goes low, the Alarm_On output should go low by the end of the next complete clock cycle.

i) Clearly describe any additional rules or assumptions.

Write a VHDL or Verilog code that implements the above alarm clock. Use one-hot encoding for state encoding. Verify the functionality and behavior of the circuit. Use Quartus II toolset. Submit a report containing the following:

1. A state diagram showing the implementation of your design (overview of your design, a detailed description of your approach and design process). Clearly show all the states and the conditions on which transitions occur.

2. Hardcopy of your code.

3. Hardcopy of annotated (properly labeled) waveforms that demonstrate all the required behavior.

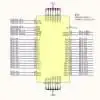

4. RTL schematic of the design after compilation.

5. Roughly, draw the implied hardware of your code. Provide a brief comparison between the tool's RTL schematic and the implied hardware you drew.

6. Extract the highest clock frequency of your design from the compilation report.

ID do Projeto: 7450047

Sobre o projeto

8 propostas

Projeto remoto

Ativo há 9 anos

Quer ganhar algum dinheiro?

Benefícios de ofertar no Freelancer

Defina seu orçamento e seu prazo

Seja pago pelo seu trabalho

Descreva sua proposta

É grátis para se inscrever e fazer ofertas em trabalhos

8 freelancers estão ofertando em média $29 USD for esse trabalho

7,8

7,8

5,8

5,8

5,1

5,1

2,1

2,1

0,0

0,0

0,0

0,0

0,0

0,0

Sobre o cliente

Bridgeport, United States

1

Método de pagamento verificado

Membro desde mar. 13, 2015

Verificação do Cliente

Outros trabalhos deste cliente

$10-30 USD

$10-30 USD

Trabalhos semelhantes

$10-30 USD

₹1500-12500 INR

₹1500-12500 INR

₹12500-37500 INR

$30-250 USD

$15-25 USD / hour

₹12500-37500 INR

$30-250 USD

$250-750 USD

₹750-1250 INR / hour

Obrigado! Te enviamos um link por e-mail para que você possa reivindicar seu crédito gratuito.

Algo deu errado ao enviar seu e-mail. Por favor, tente novamente.

Carregando pré-visualização

Permissão concedida para Geolocalização.

Sua sessão expirou e você foi desconectado. Por favor, faça login novamente.